电子微组装可靠性设计的挑战,来自两个方面:一是高密度组装的失效与控制;二是微组装可靠性的系统性设计。

一、高密度组装的失效与控制

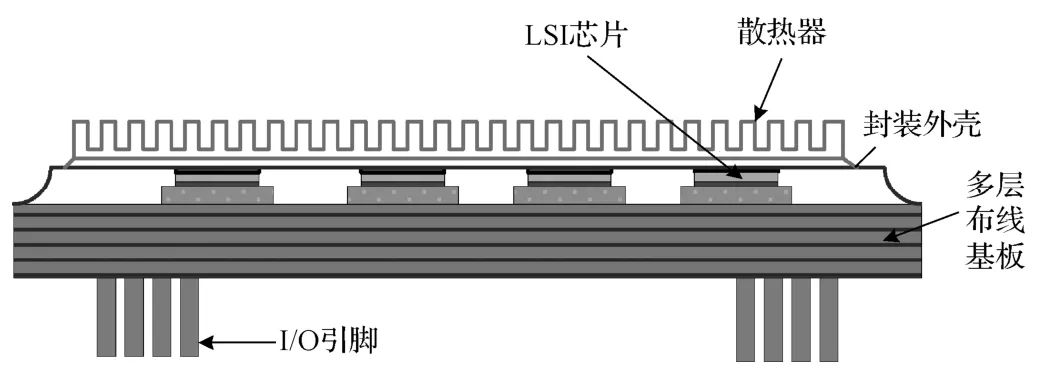

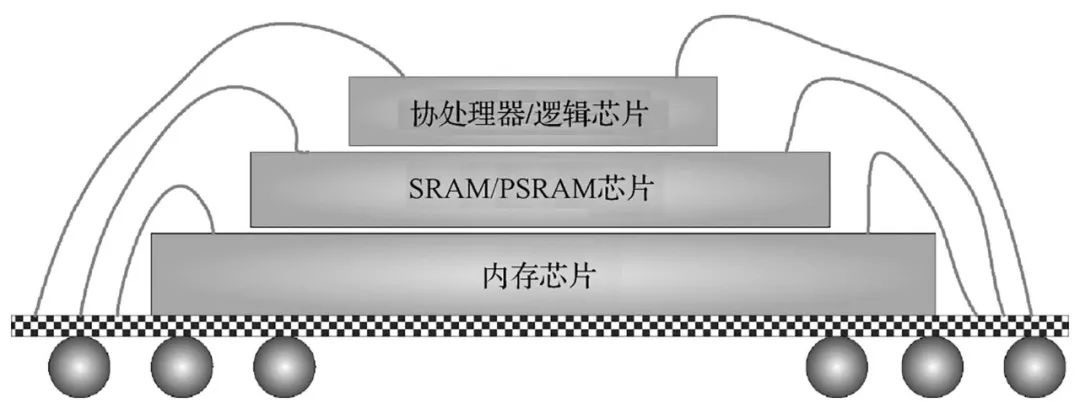

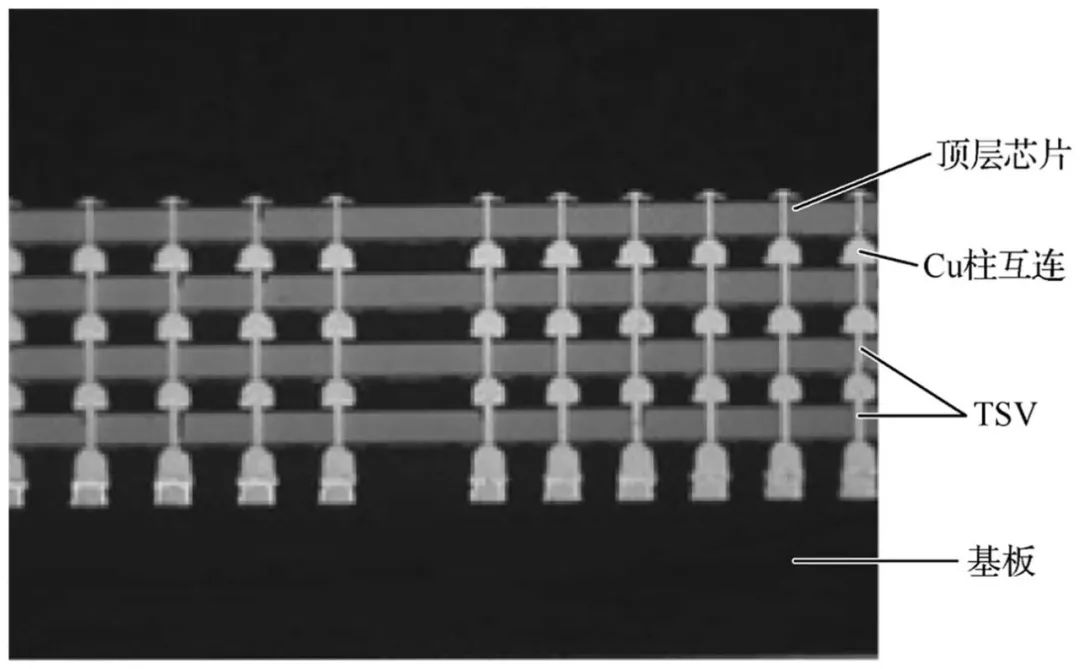

高密度组装的代表性互连模式有两类,一类是元器件高密度组装,有两种典型的芯片组装方式,即芯片并列式组装(2D)和3D-芯片堆叠组装结构叠层式,如图1和图2所示;另一类是高密度微互连,例如,3D叠层芯片TSV硅通孔、高密度低拱形丝键合,如图3和图4所示。

图1 芯片并列式组装(2D)

图2 3D-芯片堆叠组装结构

图3 3D叠层芯片TSV硅通孔

图4 3D叠层芯片高密度低拱形丝键合

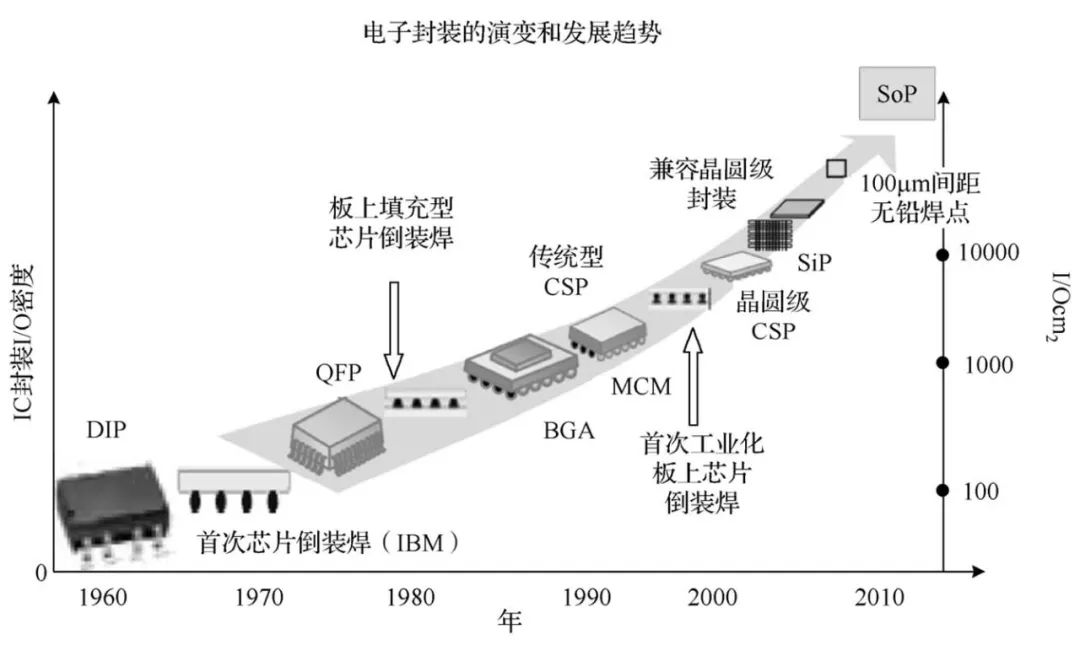

从电子微组装的发展趋势可以看出,微组装技术的发展必然带来产品的更高密度封装,而高密度封装的可靠性问题,主要是产品内部热流密度增加导致的温升、微互连间距减小导致的短路风险、封装体内元器件电磁干扰及潜在传播路径等问题。

图5 电子封装50多年的演变和发展趋势

来源链接:https://gongkong.ofweek.com/2021-01/ART-310003-11000-30481413.html

© 版权声明

本站部分资源来自于网络,仅供学习与参考,请勿用于商业用途,否则产生的一切后果将由您(转载者)自己承担!

如有侵犯您的版权,请及时联系3500663466@qq.com,我们将第一时间删除本站数据。

相关文章

暂无评论...